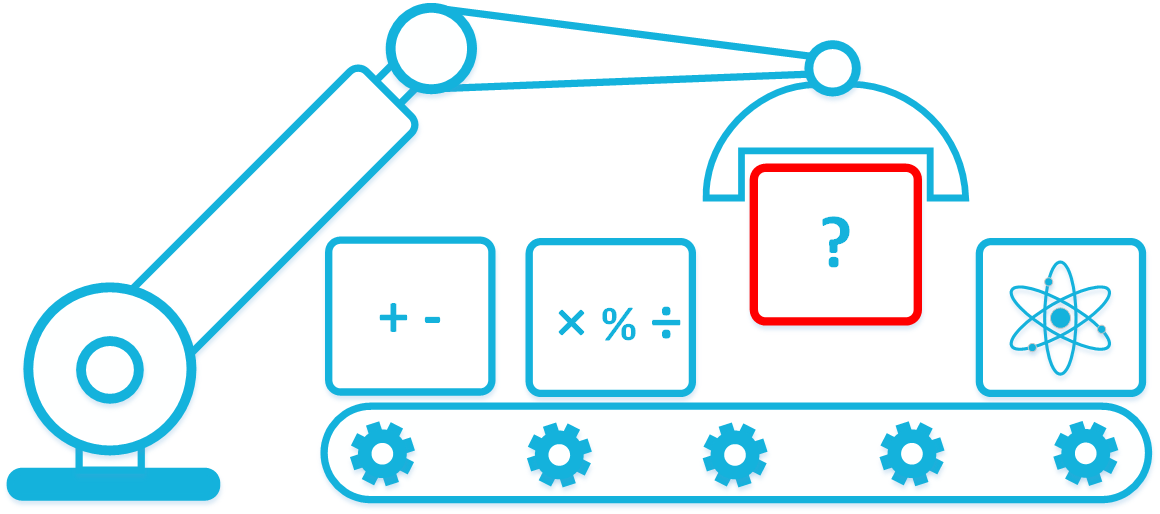

Кастомизация платформы и процессорных СФ блоков. Адаптация под требования заказчика.

- Оптимизация конвейера для требуемой технологии производства

- Улучшение производительности на сценариях заказчика за счет реализации дополнительных инструкций с полной поддержкой в компиляторе

- Разработка и/или интеграция ускорителей с процессорной подсистемой

- Интегрированные с процессором ОЗУ и кэш-памяти с различным набором параметров

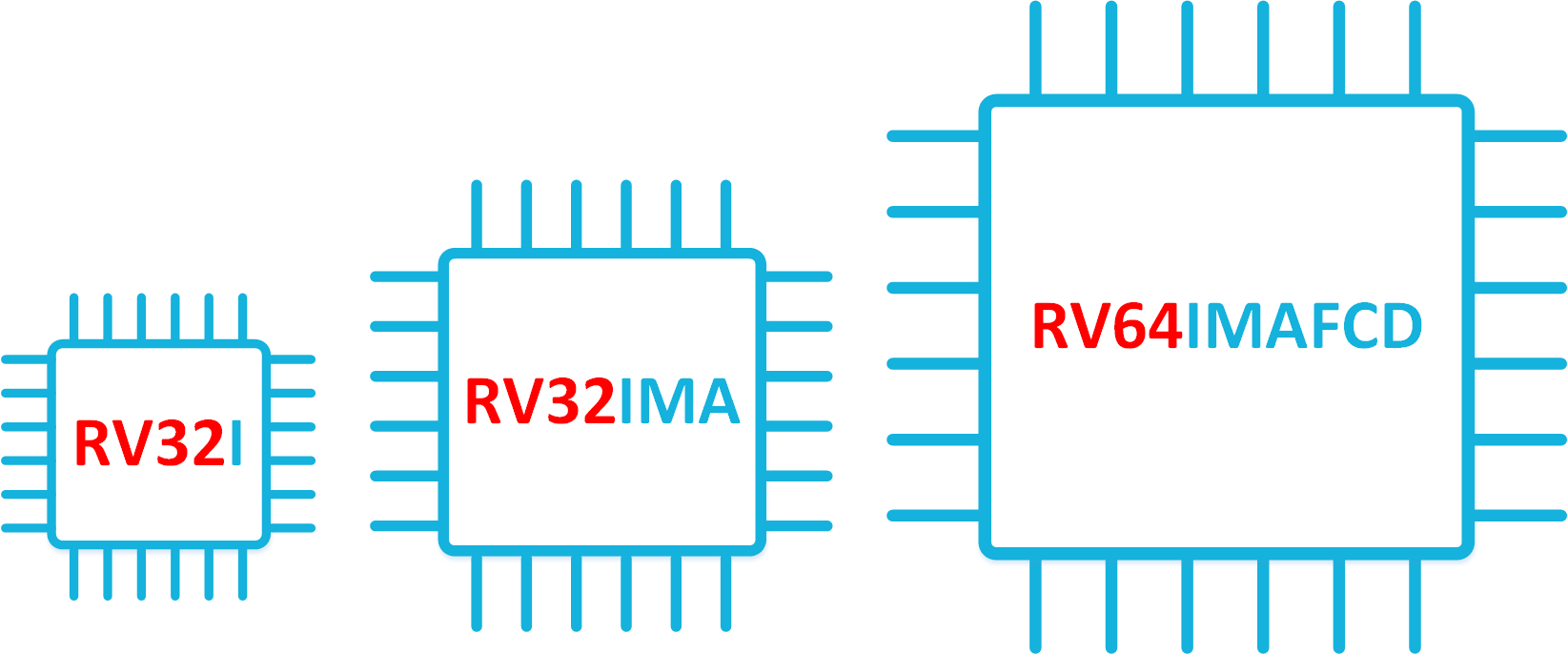

Любые расширения. Любые комбинации.

Поддержка различных комбинаций расширений системы команд RISC-V

- 32/64-битная система команд RISC-V с 32-мя регистрами (I расширение)

- Целочисленное умножение и деление (M расширение)

- Поддержка атомарных операций (A расширение)

- 16-битные инструкции для увеличения плотности кода (C расширение)

- IEEE 754-2008 совместимая плавающая точка одинарной и двойной точности (F, D расширения)

- Поддержка прерываний в User режиме привилегированности (N расширение)

- Инструкции для битовых операций (B расширение)

- Криптографические инструкции (K расширение)

- Специализированные инструкции для отечественной криптографии (Кузнечик, Стрибог, Магма)

- Инструкции для цифровой обработки сигналов (P расширение)

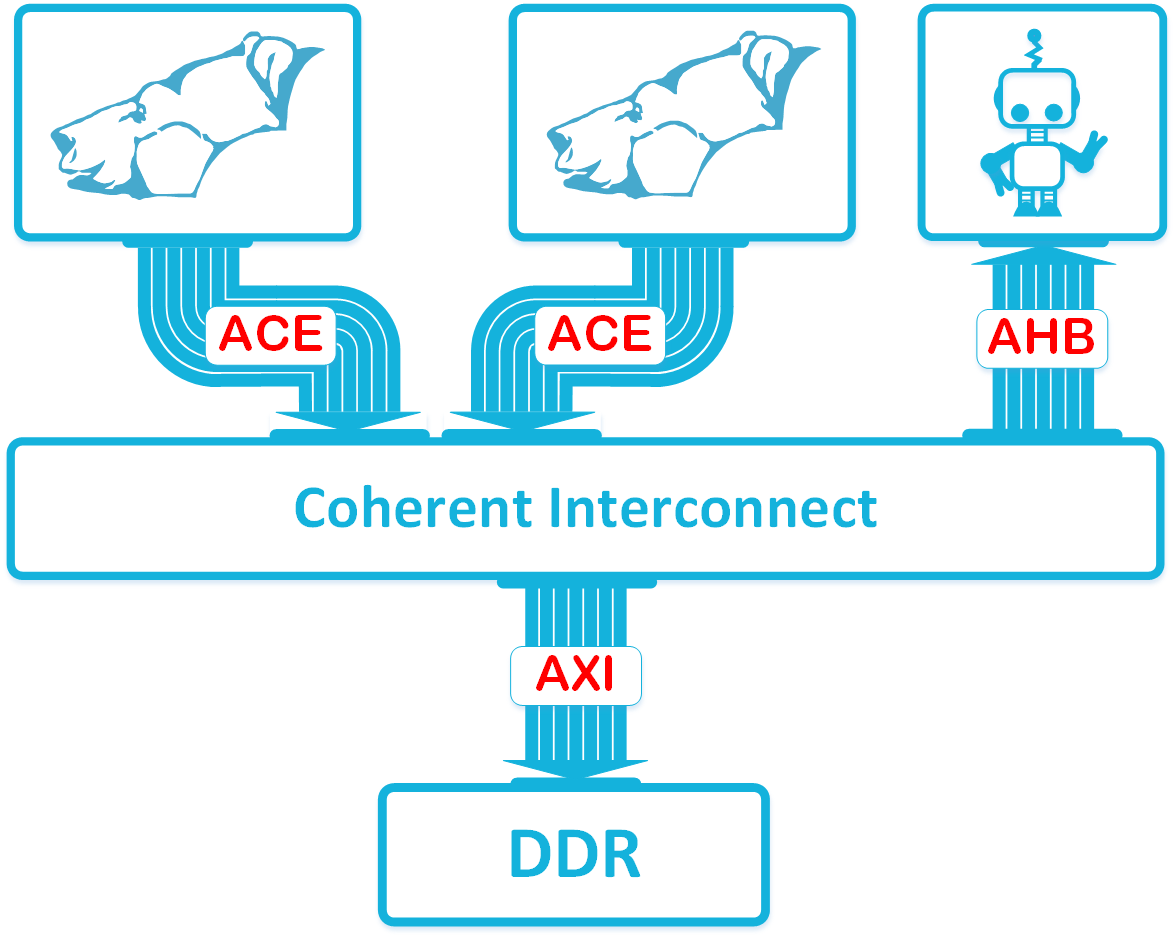

Интеграция системы-на-кристалле. AHB, AXI, ACE протоколы.

Поддержка интеграции продуктов в систему-на-кристалле заказчика. Стандартные интерфейсы систем-на-кристалле с поддержкой протоколов когерентности.

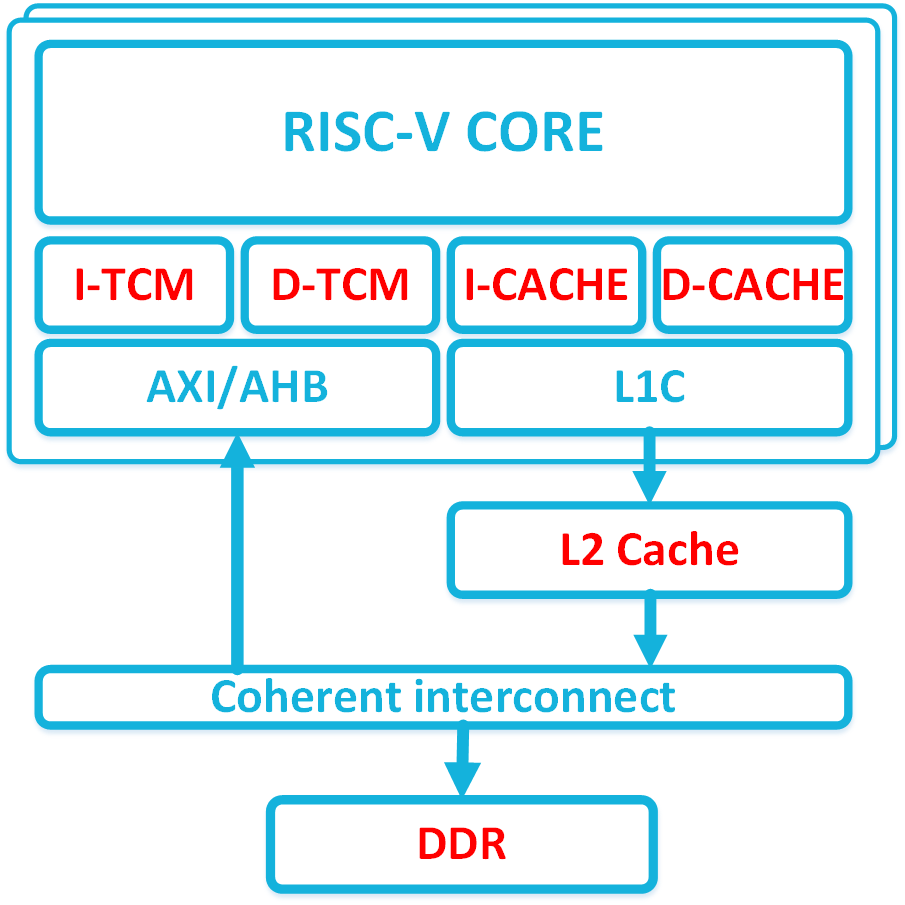

Конфигурируемая подсистема памяти. Кэш памяти, интегрированные с ядром памяти.

Конфигурируемые кэш памяти инструкций и данных. Возможность выбора размера кэша, кэш линии, ширины шин данных и размера буферов запросов. Опционально поддерживаются интегрированные с ядром памяти для приложений, требующих низкой задержки и детерминированного времени ответа.