BR-652

Gen#2 of 64-bit RISC-V compact high-performance embedded core.

Improved performance while keeping power/area the same with Gen#1.

Ideal for high performance microcontrollers, real-time control, DSP.

Gen#2 of 64-bit RISC-V compact high-performance embedded core.

Improved performance while keeping power/area the same with Gen#1.

Ideal for high performance microcontrollers, real-time control, DSP.

Support of configurable TCMs address ranges. TCM arbiter allows TCMs be accessible by fetch, load/store and via front-port. Optional instruction/data caches may be used with the following features:

Core completes all activity including cache requests and enter WFI mode. Support of external power management unit to provide clock gating and memory sleep.

Physical memory protection (PMP) is key mechanism to provide isolation between different software components and limit their access to hardware. Up to 64 PMP regions are supported in BR-652.

Preintegrated and tested subsystem is available. Flexible bus infrastructure to connect the cores itself and external world is supported. Different inter core communication mechanisms are possible:

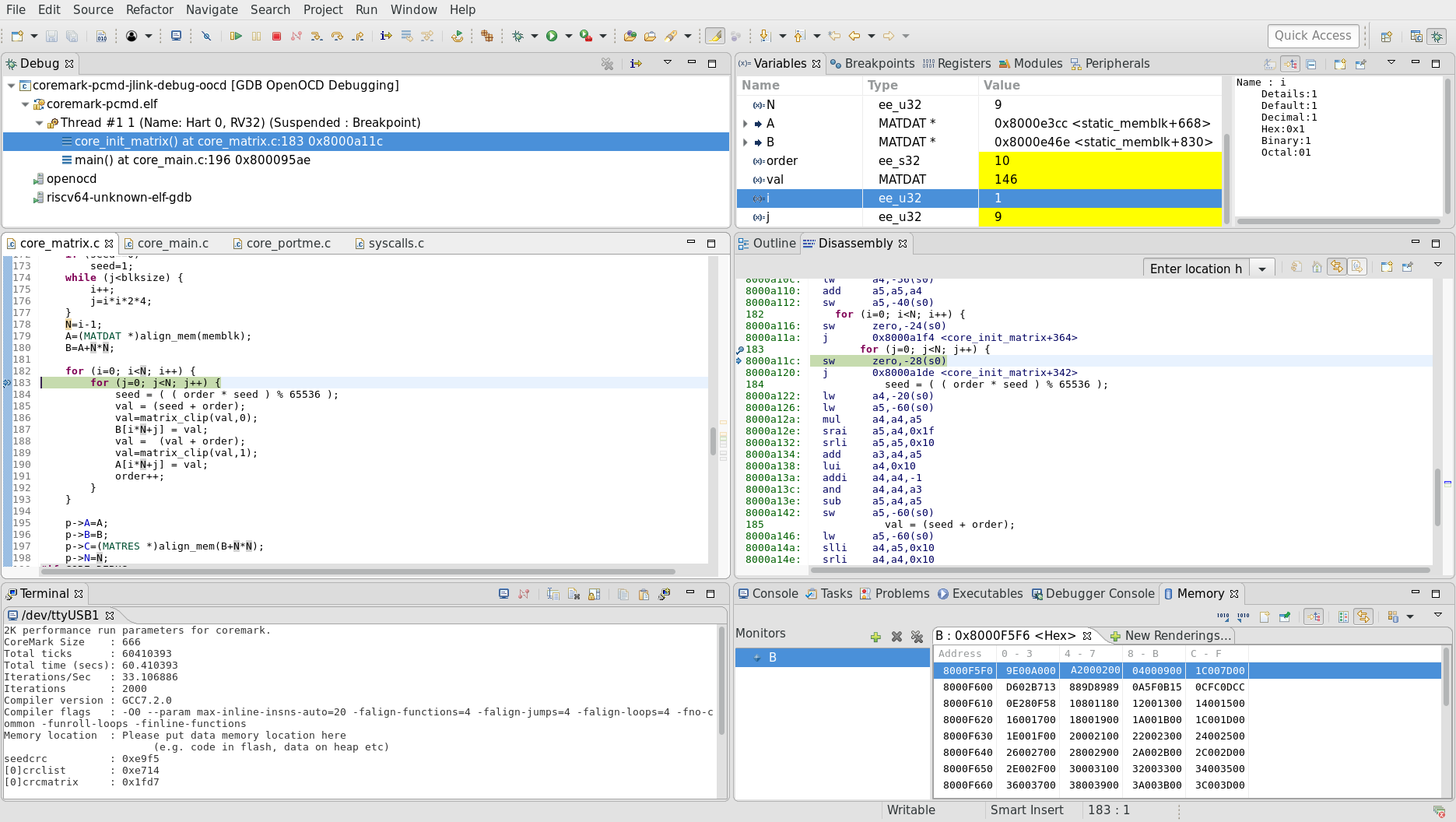

Complete set of RISC-V tools for fast and convenient software development. Compatible with upstream standard development and debug tools: OpenOCD, GCC, GDB, Eclipse. CloudBEAR also provides pre-configured Eclipse-based IDE with prebuilt toolchain and example projects for easy development start.

IAR Embedded Workbench® offers excellent optimization technology to ensure developers that the application fits the required needs and optimizes the utilization of on-board memory and necessary speed. In this first release code density is already small comparing to other available tools. However, more optimizations are expected in future releases to generate even smaller code.

SEGGER Embedded Studio for RISC-V is the development environment for devices based on the open RISC-V architecture. Embedded Studio offers a complete solution to develop and debug your application. It enables you to use the complete development solution, including toolchain, optimized run-time library, core simulator and hardware debugging with the J-Link debug probes.

TRACE32® debugger for RISC-V. Lauterbach is the world's largest producer of complete, modular and upgradeable microprocessor development tools worldwide with experience in making world class debuggers and real-time trace since 1979.

BR-652 has integrated Debug module (compliant with RISC-V specification) that allows to use most of standard debug probes. The following debug probes are verified: