Processor/platform IP customization. According to customer requirements.

- Pipeline optimization for required technology node

- Improving performance on customer workloads with custom instructions, including compiler support

- Custom accelerators design or customer accelerators tightly integration with processor cores

- Tightly coupled memories or caches in different combinations and set of options

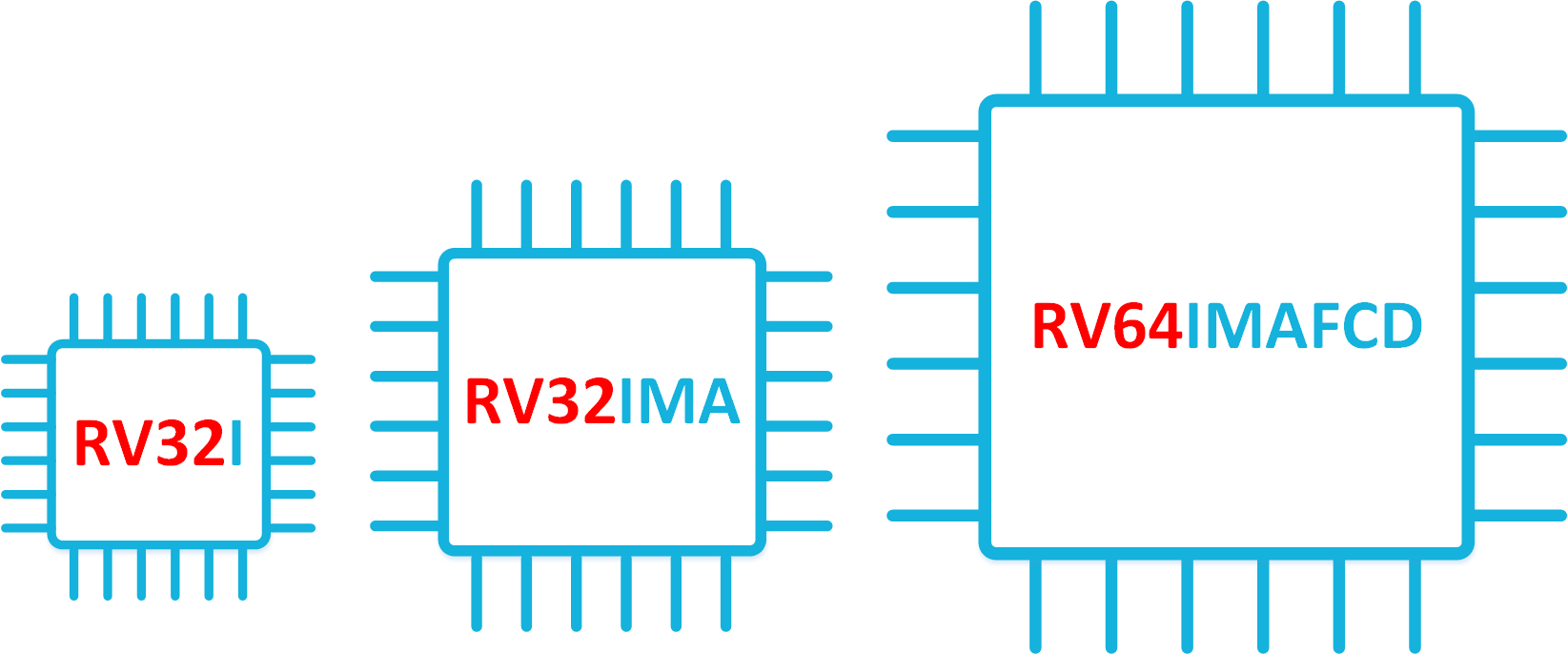

Any extensions. Any combinations.

Support of different combinations of RISC-V ISA extensions

- 32/64-bit RISC-V with 32 integer registers (I extension)

- Integer multiplication and division (M extension)

- Atomic operation support (A extension)

- Compressed mode for better code density (C extension)

- IEEE 754-2008 compliant single and double precision floating point (F, D extensions)

- User-level interrupt support (N extension)

- Bit manipulation instructions support (B extension)

- Scalar cryptography instructions support (K extension)

- Digital signal processing instructions support (P extension)

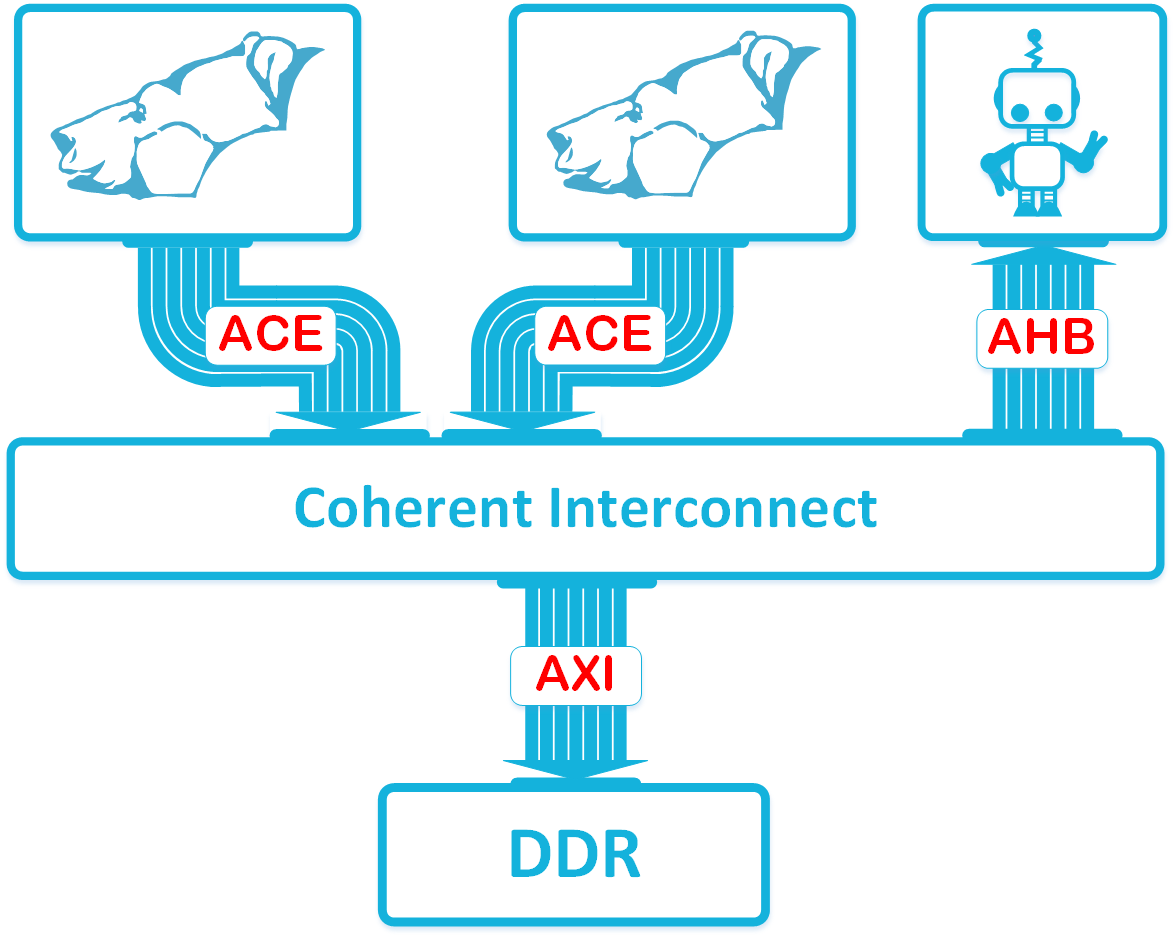

System-on-chip integration. AHB, AXI, ACE buses.

Support of the products integration within customer system-on-chip. Provide standard system-on-chip bus interfaces including coherency protocols support.

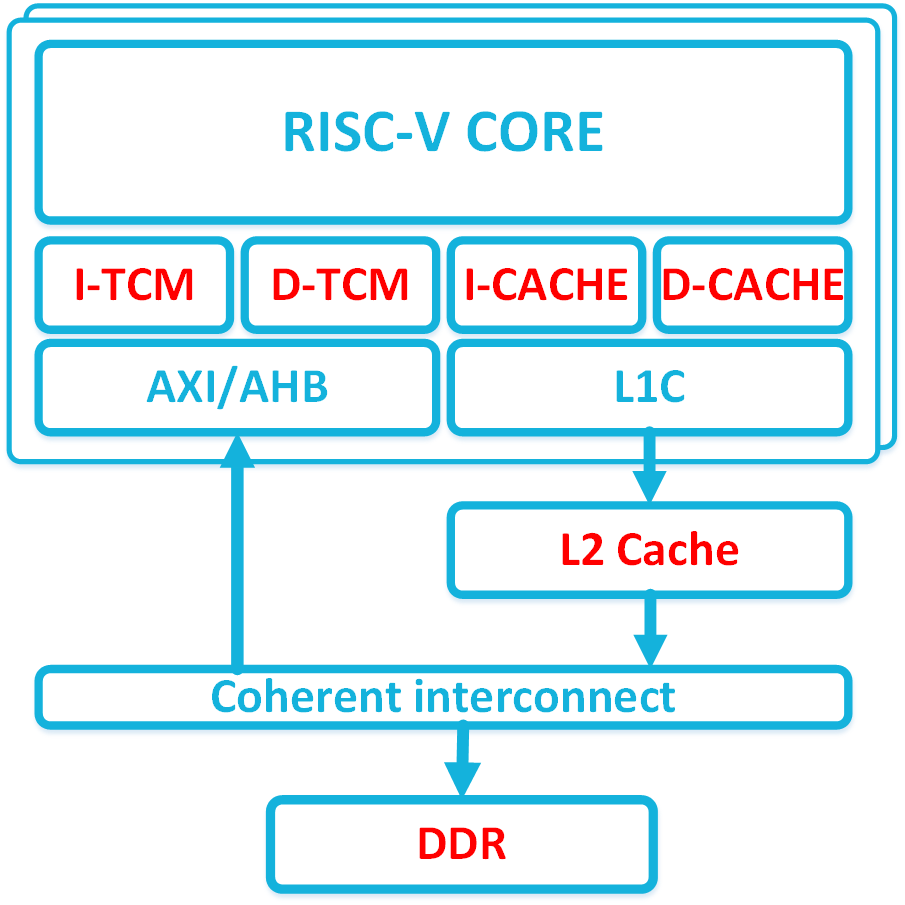

Configurable memory subsystem. Caches, Tightly coupled memories.

Configurable instruction and data caches. Selectable cache size, line width, request buffers size. Optionally tightly coupled memories are supported for application that require low-latency and deterministic response.